このページの内容は2022年1月以後保守されていません.Free EM Simulator Analyzes Spiral Inductor on Silicon

James C.RautioSonnet Software,Inc.

https://www.SonnetSoftware.com

Abstract

Si基板上のスパイラルインダクタを無料のSonnet Lite電磁界シミュレータを使って解析した. 最初に基本となるインダクタモデルを評価し、 精度を保ったまま解析速度を改善すべくモデルを単純化した. そして、 絶縁膜の厚みと誘電率、線路幅と隙間など いくつかのパラメータ に関して、インダクタの損失を改善すべく修正した. また誤差に関しても調査した.

Introduction

スパイラル インダクタはその単純形状とは裏腹に電磁界解析が困難な問題のひとつであった.さらにSi基板の導電性が問題をさらに複雑にしている. この論文ではSonnetLiteを使ってこの問題を精度よく解析する. SonnetLiteは製品版Sonnetに基づいた平面3次元電磁界シミュレータで、 無料でダウンロードできる. それはたんなるデモでなく実際に解析できるソフトウェアである. SonnetLiteは16MbyteまでのRAM(係数行列)と、2層の導体(3層の誘電体)構造を扱うことができる. またポートは4つまで許される. 多くの問題がこの制約に収まる. スパイラル インダクタもそのひとつである. Sonnetの基本アルゴリズムは導電性の誘電体の解析に理想的である. SonnetはFFT (Fast Fourier Transform) に基づく分析を行う. それゆえ、数値積分にかかわる桁落ちがない. 各層は方形導波管の集合に置き換えら得れる. 損失が与えられると各方形導波管の特性インピーダンスと伝播速度を変更する. 方形導波管のそのような性質は明確に解明されているので、基板材料に導電率が加えられても、無損失の場合と同じ精度で解析できる. Green関数を直接的に数値積分する解析方法ではこれは非常に困難である. それゆえSonnetLiteはSi基板上のスパイラルインダクタの解析に最適である.

Base Line Inductor

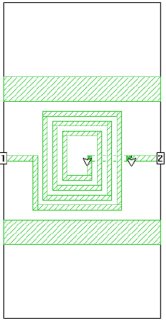

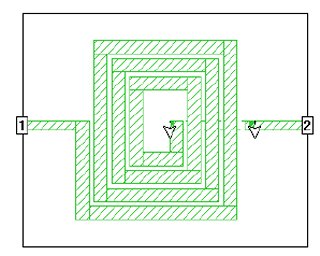

図1. 基本インダクタモデル.損失を減らすためコプレーナ構造にしている.

図1は基本インダクタモデルである. 基板損失を減らすため、コプレーナ構造を採用した. これにより電界は信号線と両側のグランド導体の間に生じ、 基板材料の内部に入り込む電界を減らすことができる.

インダクタの線路は8umで、線路間隔は8umである. 線路から両側のグランド導体までの距離は16umで、 基板はεr=12、導電率20S/mで厚さ1000umである. さらに表面にεr=4 厚さ1umのSiO2層がある. ほとんどの導体はSiO2層の表面に置かれるが、 インダクタの中心からの引き出し線だけはSiO2層と Si層の界面に置かれる. 導体の損失は(表皮効果の概算を含め) 0.04Ω/□とした.

最初の仕事は、精度を保ったままモデルを単純化することである. ソネットは金属導体の表面だけを離散化して解析し、 問題の規模が大きくなると急激にサブセクションの数が増える. それゆえ、サブセクションの数を減らすことが重要である.

まずはサブセクションの大きさを可能な限り大きくする. この問題では単純に8umのセルサイズにすればよい. これで、8um幅の線路がひとつのセルに割り当てられる. このことは誤差の原因になるかもしれないが、それについては後述する.

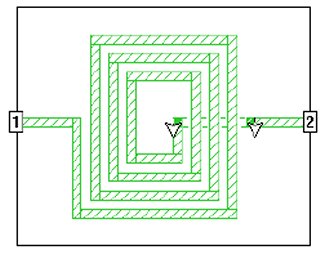

次に、導体の面積を減らしてサブセクションの数を減らす. コプレーナ線路ではグランド導体の面積が大きい. それを解析の対象から取り除くことができれば大きな効果がある. Sonnetでは側壁は完全導体なので、コプレーナ線路のグランド導体を取り除いて、 そこに側壁を置くことは容易である. そうすれば、リターン電流はグランド導体でなく、Sonnetの側壁を流れる. 側壁をインダクタの導体から24umの位置においてみよう. (グランド導体はインダクタの導体から16umの位置にあった)

図2. グランドリターン電流を側壁に流すために修正したモデル.グランド導体を取り除くと解析速度が改善される.

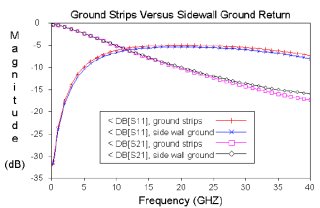

図3. 図1と図2のモデルの解析結果の比較.高い周波数でS11が約0.5dB、S21が約2.0dB違う.

これはとても大きな変更なので大きな間違いを引き起こさないか心配かもしれない. 図3はこの変更による結果を検証したグラフである.この違いは十分小さいとみなすことができるだろう.450MHzのPentiumで 図2のモデルの解析には1MByteのRAMと1周波数あたり1秒必要だった.図1のモデルでは2MByteのRAMと2秒が必要だった.

Error Bounds

ここで解析精度について考察しておこう. 電磁界解析はすべてとても高い精度を主張しているが、 エンジニアは現実の問題を解析したときの精度に関心があるだろう. さらに、定量的な誤差を予測したい. 予測された誤差と、その設計に必要な精度を比較することで、 その解析を信じるべきか否かを決定することができる.

Sonnetの誤差要因は広く分析されている. ほとんどの場合主要な誤差要因はセルサイズに起因する. そして、セルサイズを半分にすれば誤差も半分になる性質がある.

セルサイズに起因する誤差は容易に評価できる. セルサイズを半分にして誤差が半分になるならば、 その半分の誤差から、 セルサイズを無限小にした場合との誤差も知ることができる.

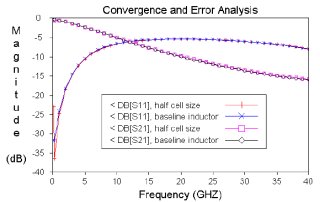

図4. セルサイズを8umから4umにしたときの誤差.ほぼ0.15dBである.したがって8umのセルサイズの結果は真値の±0.3dB以内と考えてよい.

図4はこの収束の結果である. セルサイズを8umで解析し、次に4umで解析した. この二つの結果の差は0.15dB以下であった. このことからは8umセルの結果が真値から±0.3dB以内にあるといえる.

もしこの誤差±0.3dBが十分なら、セルサイズは8umで十分である. しかし、よりよい精度を求めるなら "Richardsonの補外"を使うことができる. セルサイズ8umの各周波数でのデータから誤差(8umの場合の結果と4umの場合の結果の差の二倍)を差し引けばよいのである. Excelのようなスプレッドシートプログラムがこの計算には便利である. この処理の結果得られるデータの誤差は±0.05dBのオーダーになる.

The Lossless Limit

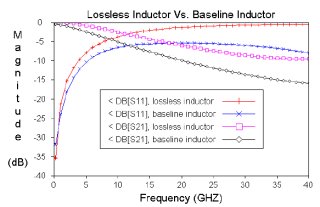

図5. 図2のモデルからあらゆる損失成分を取り除いた場合の変化.40GHzで7dB.

損失を改良するまえに、完全に損失を無くした解析を行っておく. これによって究極的にはどこまで損失を改良できるかの限界を知ることができる. 図2のモデルからすべての損失項(導体損失、誘電体損失)を取り除いた結果が図5である.

40GHzでのS11とS21の両方で概ね7dBの差がある.つまり大いに改良の余地があるということである.

Line Width

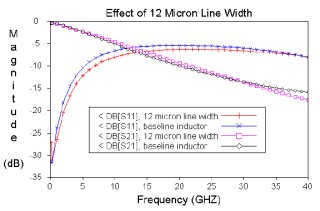

図6. 損失の効果を確かめるため線路幅を8umから12umにした.

図7. 線路幅を8umから12umにすると、意外にも損失は増加した.

図2の基本インダクタモデルを元に、線路幅を増やしてみた. 幅の広い線路の損失は少ないはずである. 線路幅を図6のように8umから12umに増やした. 結果は図7で 解析時間は1周波数辺り11秒であった. そして、意外にも損失は増加した. もちろん導体損失が減少したことは疑うべくもないが、 それ以上に誘電体損失が増加したのであろう.

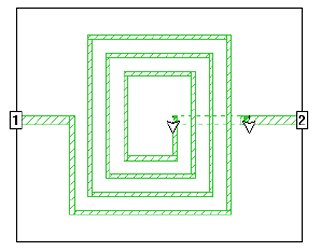

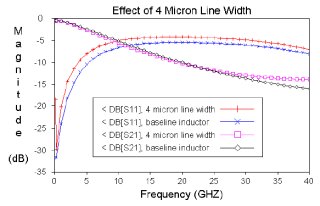

図8. 線路幅を8umから4umにした.

図9. 線路幅を8umから4umにすると、損失は改善した.

図8は線路幅を4umに狭めたモデルで、図9が解析結果である.(解析時間は1周波数あたり5秒) 損失は改良されている. 必要なら、さらに線路幅は最適化できるだろう.

Insulating Layer Thickness and Dielectric Constant

スパイラル インダクタはSi層の上にSiO2などの絶縁膜を介して配置される. これはSi基板の導電性の効果を特に低い周波数で低減する. この絶縁膜を厚く、そして低誘電率にすることはインダクタの損失を改良する.

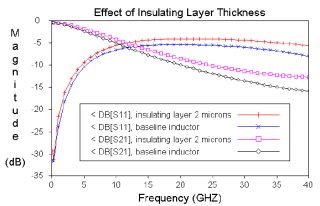

図10. SiO2層の厚さを1umから2umにすると損失は明確に低下する.

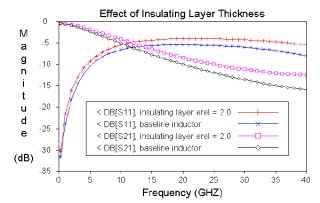

図11. SiO2層の誘電率を4から2にすると損失は明確に低下する.

この方法を確かめるべく、 まず、絶縁膜SiO2の厚さを1umから2umにした.図10がその結果である. 次に、絶縁膜の誘電率を4から2にした.図11がその結果である. どちらの場合も全周波数域で損失が改良されている.

さてこれで、損失を改善する各パラメータの傾向を把握できた. そして、設計と製造上の制約を考慮すれば、 設計者は損失を最小にする設計を実現できるだろう.

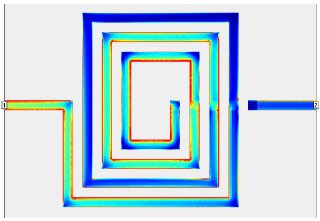

図12. 基本インダクタモデルを0.5umの細かいセルサイズで解析した電流分布. インダクタ中心からの引き出し線の効果がリアルに現れている.

スパイラルインダクタの設計についてさらに洞察を進めるべく、0.5umの細かいセルを使った解析を試みた. この解析には製品版のSonnetを使い、各線路幅あたり16のセルを使った. 図12はその電流分布の解析結果である. インダクタの引き出し線と交差する部分に電流分布の乱れが観察できる.

図12では、赤い部分は1200A/mである. port1には40GHzの内部抵抗50Ωの1Vの電圧源が接続されている. port2は50Ωで終端されている. 解析には12000以上のサブセクションと305MbyteのRAMを必要とした. 使用したPCは256MbyteのRAMしか実装していなかったのでSWAPを起こし、 解析には8時間を必要とした. (訳注:この記事が最初に書かれてから以後、PCとSonnetのコードの両方が著しく進歩した結果、現在ではこの問題は 3.6GHzのPentiumで 1周波数あたり3分、40GHzまでの周波数特性の解析に23分で解析できる)

Conclusion

Si上のスパイラルインダクタの解析に無料の電磁界シミュレータSonnetLiteが使えることを示した. さらに, インダクタの損失を改良する方法を示し、解析誤差の分析を行い、 製品版のSonnetを使うことなく誤差を予測するために "Richardsonの補外"を行った. 以上に説明した方法で、あらゆる3次元電磁界問題をSonnetLiteが有用であると考える.

Acknowledgement

Sonnet Lite was made possible because of work funded by DARPA under the MAFET program.

訳

石飛徳昌

(有)ソネット技研

https://www.Sonnet.Site

2006/9/14